——Nozaraina avy amin'ny DWIN Froum

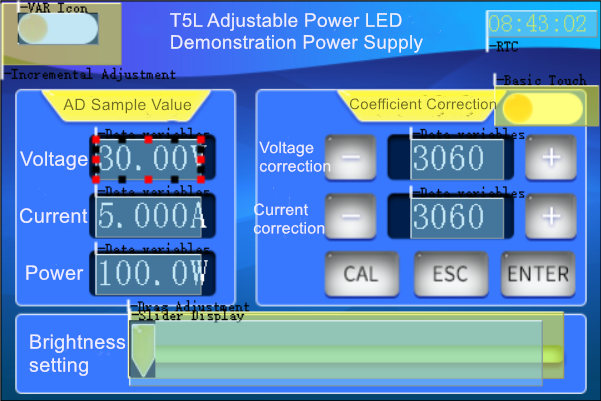

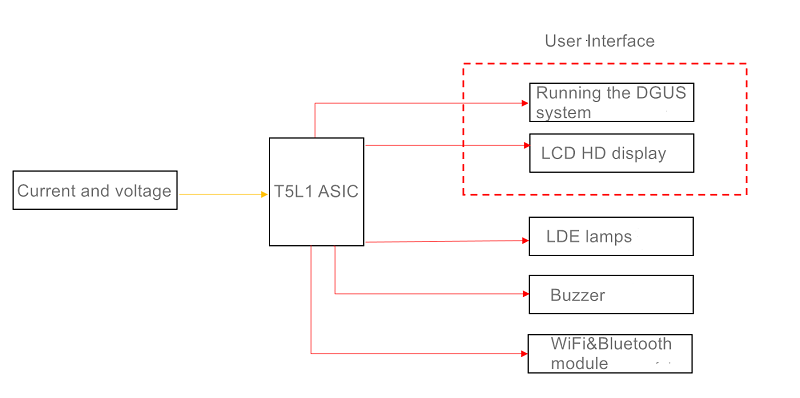

Ny fampiasana ny chip DWIN T5L1 ho fototry ny fanaraha-maso ny milina iray manontolo, dia mandray sy manodina ny fikasihana, ny fahazoana ADC, ny fampahalalana momba ny fanaraha-maso PWM, ary mitondra ny efijery LCD 3.5-inch hanehoana ny sata ankehitriny amin'ny fotoana tena izy.Tohano ny fanitsiana lavitr'ezaka amin'ny famirapiratan'ny hazavana LED amin'ny alàlan'ny module WiFi, ary manohana ny fanairana feo.

Endri-javatra fandaharana:

1. Raiso T5L chip mba hihazakazaka amin'ny avo matetika, AD analog sampling dia miorina tsara, ary ny fahadisoana dia kely;

2. Support TYPE C mifandray mivantana amin'ny PC ho an'ny debugging sy ny fandoroana fandaharana;

3. Tohano ny interface tsara OS core, 16bit parallèle port;UI core PWM seranan-tsambo, AD seranan-tsambo nitarika, mora vidy fampiharana famolavolana, tsy mila manampy fanampiny MCU;

4. Tohano WiFi, fanaraha-maso lavitra Bluetooth;

5. Manohana 5 ~ 12V DC midadasika midadasika sy midadasika fidirana

1.1 Diagrama tetika

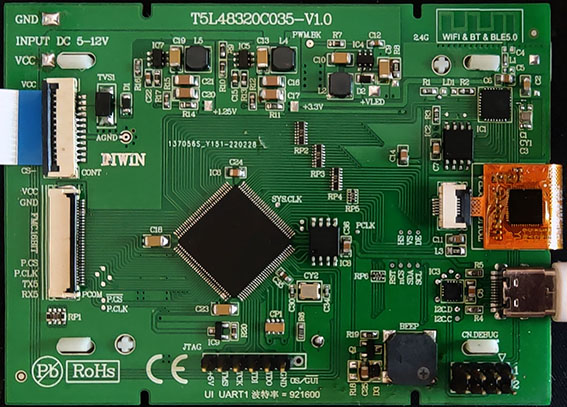

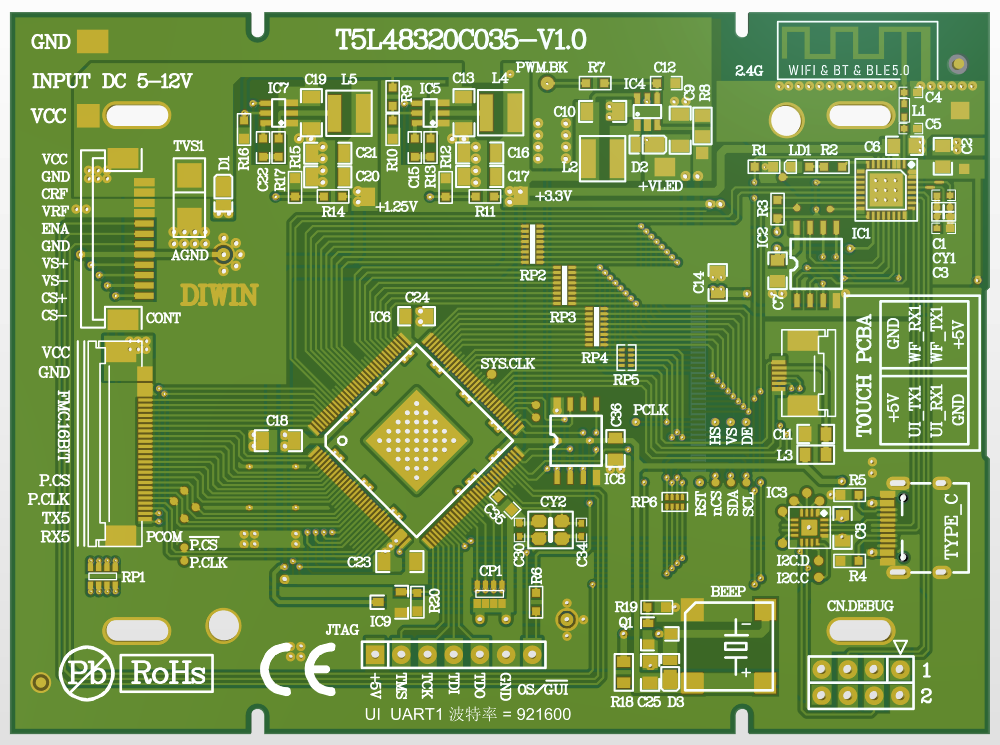

1.2 PCB board

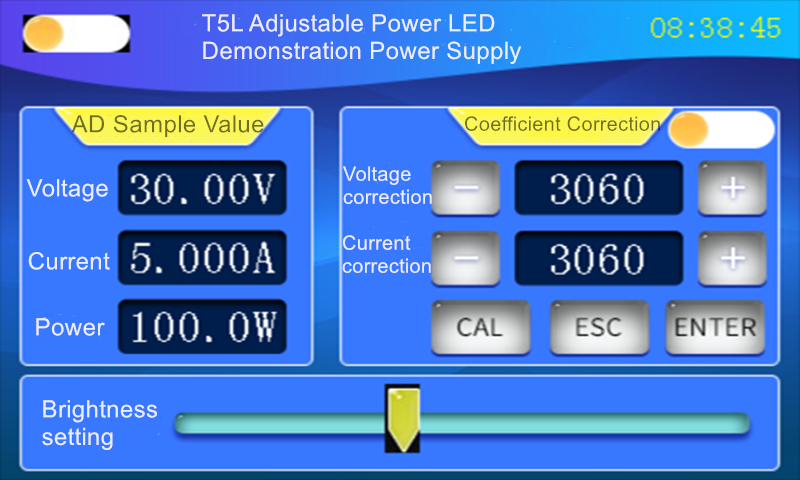

1.3 User interface tsara

Fampidirana mahamenatra:

(1)Ny fandrafetana rindrankajy

Sary 1.4 T5L48320C035

1. MCU lojika famatsiana herinaratra 3.3V: C18, C26, C27, C28, C29, C31, C32, C33;

2. Famatsiana herinaratra fototra MCU 1.25V: C23, C24;

3. MCU famatsiana herinaratra analogue 3.3V: C35 no famatsiana herinaratra analogue ho an'ny MCU.Rehefa fehezina dia azo atambatra ny tany 1.25V fototra sy ny tany lojika, fa tsy maintsy misaraka ny tany analoga.Ny tany Analog sy ny tany nomerika dia tokony ho angonina amin'ny tsato-kazo ratsy ny LDO Output lehibe capacitor, ary ny Analog tsara tsato-kazo ihany koa dia tokony ho nangonina amin'ny tsara tsato-kazo ny LDO lehibe capacitor, ka AD sampling Noise dia kely kokoa.

4. AD analog signal acquisition circuit: CP1 no AD analog input filter capacitor.Mba hampihenana ny fahadisoana santionany dia misaraka tsy miankina ny tany analog sy ny tany nomerika an'ny MCU.Ny tsato-kazo ratsy an'ny CP1 dia tsy maintsy ampifandraisina amin'ny tany analoga amin'ny MCU miaraka amin'ny impedance kely indrindra, ary ny capacitors roa mifanitsy amin'ny oscillator kristaly dia mifandray amin'ny tany analogue an'ny MCU.

5. Circuit buzzer: C25 no capacitor famatsiana herinaratra ho an'ny buzzer.Ny buzzer dia fitaovana inductive, ary hisy ny rivo-mahery mandritra ny fandidiana.Mba hampihenana ny tampon'isa, dia ilaina ny mampihena ny MOS fiara amin'izao fotoana izao ny buzzer mba hahatonga ny MOS fantsona miasa ao amin'ny linear faritra, ary mamolavola ny faritra mba hahatonga azy io hiasa amin'ny fomba switch.Mariho fa ny R18 dia tokony ampifandraisina mifanitsy amin'ny tendrony roa amin'ny buzzer mba hanitsiana ny kalitaon'ny feon'ny buzzer ary hahatonga ny feon'ny buzzer ho malefaka sy mahafinaritra.

6. Wi-Fi circuit: WiFi chip sampling ESP32-C, miaraka amin'ny WiFi + Bluetooth + BLE.Eo amin'ny tariby dia misaraka ny sisin'ny herinaratra RF sy ny tany famantarana.

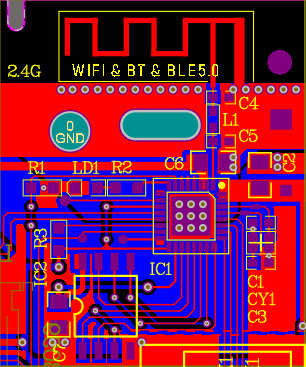

1.5 famolavolana faritra WiFi

Ao amin'ny sary etsy ambony, ny tapany ambony amin'ny coating varahina dia ny loop ground power.Tsy maintsy manana faritra midadasika mankany amin'ny toeram-pamokarana herinaratra ny tadin'ny antenne WiFi, ary ny teboka fanangonan'ny tobin-jiro dia ny tsato-kazo ratsy C6.Mila apetraka eo anelanelan'ny tobin-jiro sy ny antenne WiFi ny taratra ankehitriny, noho izany dia tsy maintsy misy coating varahina eo ambanin'ny antena WiFi.Ny halavan'ny coating varahina dia mihoatra ny halavan'ny fanitarana ny antenne WiFi, ary ny fanitarana dia hampitombo ny fahatsapana ny WiFi;manondro ny tsato-kazo ratsy C2.Ny faritra lehibe amin'ny varahina dia afaka miaro ny tabataba vokatry ny taratra antenne WiFi.Ny tany varahina 2 dia misaraka amin'ny sosona ambany ary angonina amin'ny pad afovoan'ny ESP32-C amin'ny alàlan'ny vias.Ny tany herinaratra RF dia mila impedance ambany kokoa noho ny loop ground signal, noho izany dia misy vias 6 avy amin'ny tany herinaratra mankany amin'ny pad chip mba hiantohana ny impedance ambany.Ny tadin'ny oscillator kristaly dia tsy afaka manana hery RF mikoriana ao aminy, raha tsy izany dia hiteraka jitter matetika ny oscillator kristaly, ary tsy afaka mandefa sy mandray data ny fatran'ny WiFi matetika.

7. Backlight LED famatsiana herinaratra faritra: SOT23-6LED mpamily chip sampling.Ny famatsiana herinaratra DC/DC amin'ny LED dia mamorona tady tsy miankina, ary ny tany DC/DC dia mifandray amin'ny tany 3.3V LOD.Koa satria ny fototry ny seranan-tsambo PWM2 dia manokana, dia mamoaka famantarana 600K PWM izy io, ary ampiana RC iray hampiasa ny famoahana PWM ho fanaraha-maso ON/OFF.

8. Voltage input range: roa DC/DC step-downs dia natao.Mariho fa ny resistors R13 sy R17 ao amin'ny faritra DC/DC dia tsy azo esorina.Ny tsipika DC/DC roa dia manohana hatramin'ny 18V input, izay mety amin'ny famatsiana herinaratra ivelany.

9. USB TYPE C debug port: TYPE C dia azo atsofoka sy esorina mandroso sy miverina.Ny fampidirana mandroso dia mifandray amin'ny chip WIFI ESP32-C amin'ny programa ny chip WIFI;Ireo singa mifandraika amin'ny XR21V1410IL16TYPE C dia manohana famatsiana herinaratra 5V.

10. Fifandraisana amin'ny seranana parallèle: Ny fototry ny T5L OS dia manana seranan-tsambo IO maimaim-poana maro, ary azo atao ny mamolavola fifandraisana amin'ny seranana parallèle 16bit.Miaraka amin'ny protocol port parallèle ST ARM FMC, dia manohana ny famakiana sy fanoratana synchronous.

11. LCM RGB famolavolana interface tsara: T5L RGB Output dia mifandray mivantana amin'ny LCM RGB, ary ny buffer fanoherana dia ampiana eo afovoany mba hampihenana ny LCM rano ripple fitsabahana.Rehefa wiring, mampihena ny halavan'ny RGB fifandraisana interface tsara, indrindra fa ny PCLK famantarana, ary hampitombo ny RGB interface tsara PCLK, HS, VS, DE fitsapana teboka;ny seranan-tsambo SPI amin'ny efijery dia mifandray amin'ny seranan-tsambo P2.4 ~ P2.7 amin'ny T5L, izay mety amin'ny famolavolana ny mpamily efijery.Tariho ireo teboka fitsapana RST, nCS, SDA, SCI hanamora ny fampivoarana ny rindrambaiko fototra.

(2) DGUS interface tsara

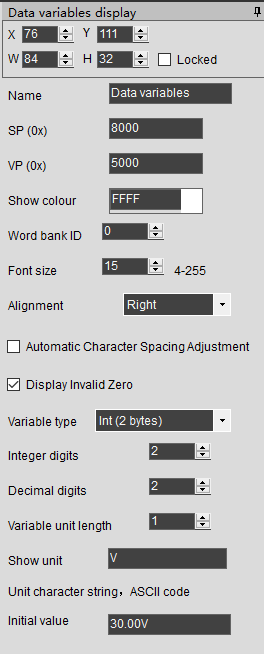

1.6 Fanaraha-maso fampisehoana miovaova angon-drakitra

(3) OS

//——————————— DGUS mamaky sy manoratra format

typedef struct

{

u16 addr;// Adiresy miovaova UI 16bit

u8 datLen;//8bitdata halavany

u8 *pBuf;// 8bit data pointer

} UI_packTypeDef;//DGUS mamaky sy manoratra fonosana

//——————————--ny fanaraha-maso ny fiovaovan'ny data

typedef struct

{

u16 VP;

u16 X;

u16 Y;

u16 Loko;

u8 Lib_ID;

u8 Haben'ny soratra;

u8 Algnment;

u8 IntNum;

u8 DecNum;

u8 karazana;

u8 LenUint;

u8 StringUinit[11];

} Number_spTypeDef;// firafitry ny famaritana data miovaova

typedef struct

{

Number_spTypeDef sp;// mamaritra SP famaritana pointer

UI_packTypeDef spPack;// mamaritra SP variable DGUS mamaky sy manoratra fonosana

UI_packTypeDef vpPack;//farito ny vp variable DGUS mamaky sy manoratra fonosana

} Number_HandleTypeDef;//data variable structure

Miaraka amin'ny famaritana fikirakirana miovaova angona teo aloha.Manaraka, mamaritra ny fari-piainana ho an'ny fampisehoana santionany volt:

Number_HandleTypeDef Hsample;

u16 voly_sample;

Voalohany, tanteraho ny asa fanombohana

NumberSP_Init(&Hsample,voltage_sample,0×8000);//0×8000 eto ny tondro famaritana

//——Data variables mampiseho SP pointer structure initialization——

void NumberSP_Init(Number_HandleTypeDef *numera,u8 *value,u16 numberAddr)

{

laharana->spPack.addr = numberAddr;

laharana->spPack.datLen = sizeof(number->sp);

laharana->spPack.pBuf = (u8 *)&numera->sp;

Read_Dgus(&numera->spPack);

laharana->vpPack.addr = laharana->sp.VP;

switch(number->sp.Type) //Ny halavan'ny data amin'ny variable vp dia voafantina ho azy araka ny karazana varimbazaha natao tao amin'ny interface DGUS.

{

tranga 0:

tranga 5:

laharana->vpPack.datLen = 2;

tapaka;

tranga 1:

tranga 2:

tranga 3:

tranga 6:

laharana->vpPack.datLen = 4;

tranga 4:

laharana->vpPack.datLen = 8;

tapaka;

}

laharana->vpPack.pBuf = sanda;

}

Aorian'ny fanombohana, ny Hsample.sp dia ny fanondro fanondroana ny fari-pahaizan'ny angon-drakitra santionany;Hsample.spPack no tondro fifandraisana misy eo amin'ny fototry ny OS sy ny fari-pahaizan'ny angon-drakitra santionany UI amin'ny alàlan'ny fiasa DGUS;Ny Hsample.vpPack dia ny toetra manova ny fari-pahaizan'ny angon-drakitra santionany, toy ny lokon'ny endritsoratra, sns., dia alefa any amin'ny fototry ny UI amin'ny alàlan'ny fiasan'ny interface DGUS.Hsample.vpPack.addr dia adiresy miovaova angon-drakitra santionany, izay azo avy hatrany avy amin'ny asa fanombohana.Rehefa manova ny adiresy miovaova na karazana data miovaova ao amin'ny interface DGUS ianao, dia tsy ilaina ny manavao ny adiresy miovaova ao amin'ny OS core synchronously.Aorian'ny fanisan'ny fototry ny OS ny fari-bolan'ny voltage_sample, dia mila manatanteraka ny asa Write_Dgus(&Hsample.vpPack) ihany izy mba hanavao izany.Tsy ilaina ny manangona ny santionany_volta ho an'ny fifindran'ny DGUS.

Fotoana fandefasana: Jun-15-2022