ASIC fampidirana

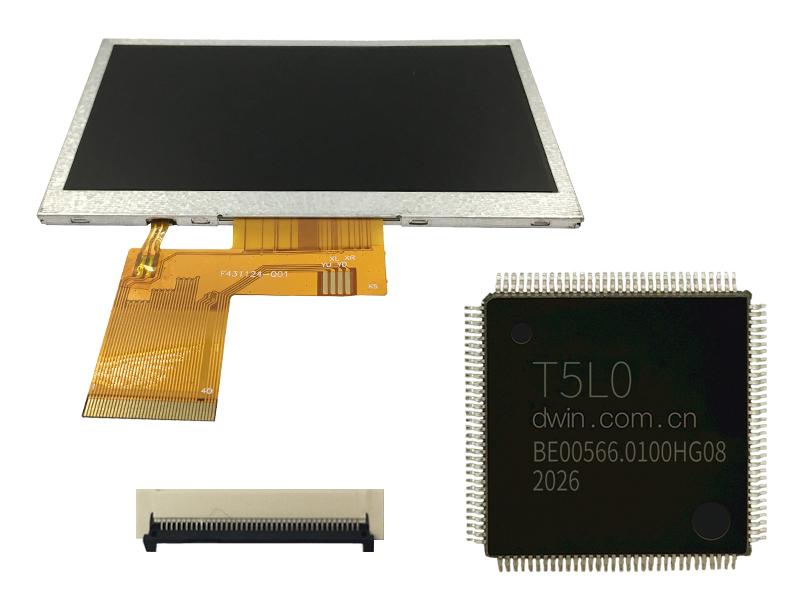

Ny andiany T5L dia ny DGUS II dual-core ASIC.

●Fanafainganana fitaovana 2D naorina

●2.4GBytes/s haingam-pandeha MB

●Tohano ny fampivoarana sy ny simulation PC configuration

●Tohano ny fanavaozana lavitra backend

●Tohano ny fanavaozana kaody an-tserasera amin'ny rafitra DGUS

●Fifandraisana manankarena ao anatin'izany ny 28IOs, 4 UARTs, 1 CAN, 8 12-bit (manohana santionany mihoatra ny 16bit) A/Ds ary 2 16-bit PWMs

SL kit

| SLE028A | T5L0+40Pin socket+2.8-mirefy 320*240 EWV(LN32240T028SA50) |

| SLI035A | T5L0+40Pin socket+3.5-mirefy 320*480 IPS(LI48320T035IA30) |

| SLI040A | T5L0+40Pin socket+4.0-mirefy 480*800 IPS(LI48800T040HA50) |

| SLI040B | T5L0+50Pin socket+4.0-mirefy 480*480 IPS(LI48480T040HA30) |

| SLI043A | T5L0+40Pin socket+4.3-inch 480*800 IPS(LI48800T043TA30 horizontaly, 480*270 koa misy) |

| SLI043B | T5L0+40Pin socket+4.3-mirefy 480*800 IPS(LI48800T043TB30 mitsangana, bezela tery) |

| SLE043A | T5L0+40Pin faladia+4.3-mirefy 480*272 EWV(LN48272T043IB35) |

| SLC043A | T5L0+40Pin socket+4.3-mirefy 480*272 TV(LN48272C043BA25) |

| SLI050A | T5L0+40Pin socket+5.0-mirefy 480*854 IPS(LI85480T050HD45) |

| SLC070A | T5L0+50Pin socket+7.0-mirefy 800*480 TV(LN80480C070BA20) |

(SLE043A)

(SLI040B)

Ny endri-javatra fototra

●ASIC noforonin-tena.

●Vidiny feno sy kalitao avo lenta.

●Volabe fandefasana entana sy famatsiana ara-potoana.

●Mety amin'ny mpanjifa manana fahaiza-manao fampandrosoana.

T5L ASIC+LCM+periferika

Dual-fototra T5L mampiasa 8051 fototra afaka mahatratra ny tena matetika matetika ny 350MHz (T5L1/2) sy 400MHz (T5L0) taorian'ny Integrated famolavolana.

Ny fototry ny GUI sy ny fototry ny OS dia mandeha tsy miankina.Ny fototry ny GUI dia mahatsapa ny fampisehoana LCD raha ny fototry ny OS dia novolavolaina mba hampiharana ny fanaraha-maso ny periferika toy ny relay sy sensor amin'ny alàlan'ny IO, AD, PWM ary interface hafa.

T5L ASIC+LCM+TP+periferika

Ny fototra T5L ASIC GUI dia mitarika amin'ny fikasihana pin, izay azo ampifandraisina haingana amin'ny TP mba hifehezana ny RTP na CTP, ary hahatsapa ny fampiratiana mitambatra sy ny fanaraha-maso mikasika ny fampifanarahana ny LCM sy ny endrika fanaraha-maso lehibe.

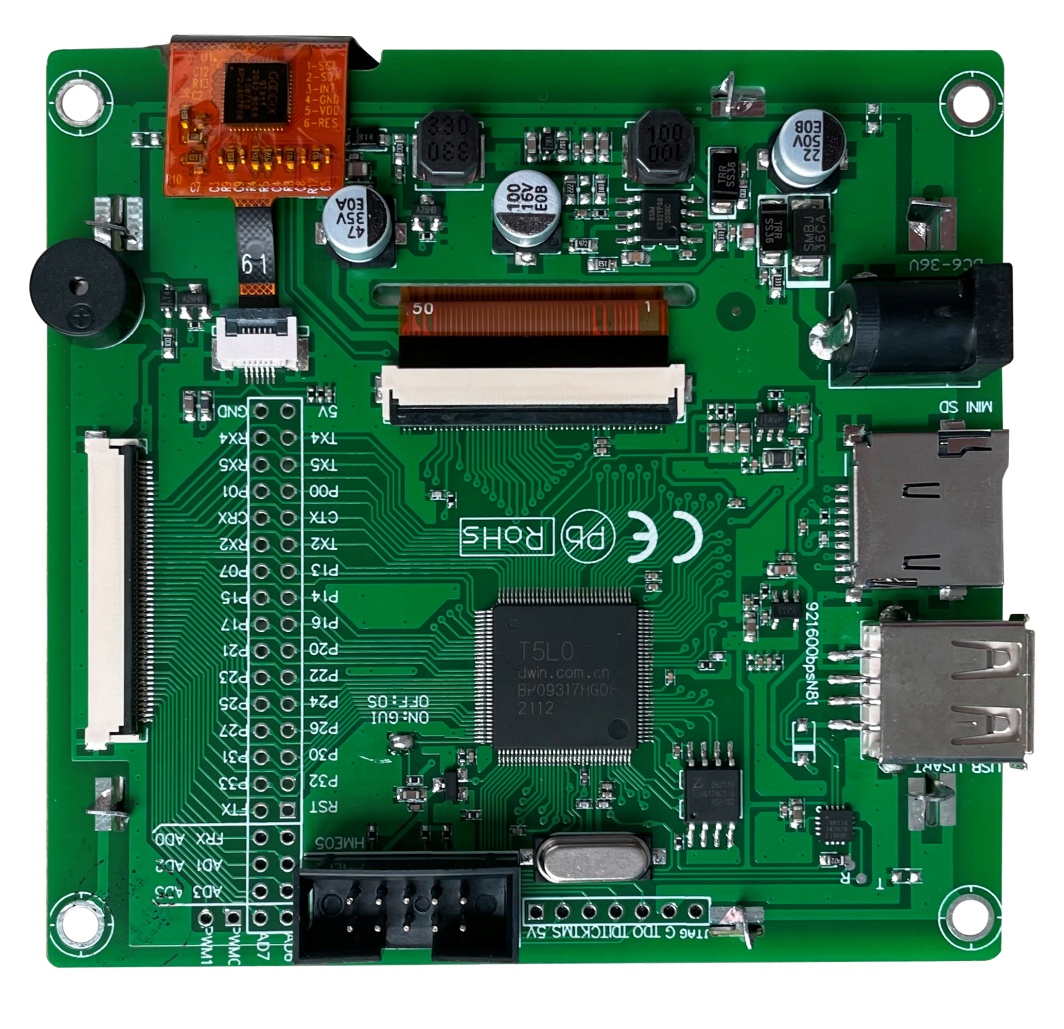

Birao fampandrosoana

Raha liana amin'ny vahaolana amin'ny efijery DWIN ASIC + ianao, ny birao fampandrosoana dia safidy tsara hahafantarana ny fomba fampandrosoana.

| Type | MODELY | Takela-daza | Sary 3D | fanamarihana |

| WTC | WTC | |||

| TA/DGUS II | EKT028 | √ | √ | T5L0 ASIC 2.8-mirefy, 240×320, loko 262K, TN |

| TA/DGUS II | EKT035A | √ | × | T5L0 ASIC 3.5-mirefy, 320×240, loko 262K, IPS |

| TA/DGUS II | EKT035B | √ | × | T5L0 ASIC 3.5-mirefy, 480×320, loko 262K, IPS |

| TA/DGUS II | EKT040A | √ | × | T5L0 ASIC 4.0-mirefy, 480×480, loko 262K, IPS |

| TA/DGUS II | EKT040B | √ | × | T5L0 ASIC 4.0-mirefy, 800×480, loko 262K, IPS |

| TA/DGUS II | EKT041 | √ | × | T5L1 ASIC 4.1-mirefy, 720×720, loko 16.7M, IPS |

| TA/DGUS II | EKT043 | √ | × | T5L1 ASIC 4.3-mirefy, 480×272, loko 16.7M, TN |

| TA/DGUS II | EKT043B | √ | × | T5L0 ASIC 4.3-mirefy, 480×800, loko 262K, IPS |

| TA/DGUS II | EKT043C | √ | × | T5L0 ASIC 4.3-mirefy, 480×272, loko 262K, TN |

| TA/DGUS II | EKT043D | √ | × | T5L0 ASIC 4.3-mirefy, 480×800, loko 262K, IPS |

| TA/DGUS II | EKT043E | √ | × | T5L0 ASIC 4.3-mirefy, 800×480, loko 262K, IPS |

| TA/DGUS II | EKT050A | √ | × | T5L0 ASIC 5.0-mirefy, 800×480, loko 262K, TN |

| TA/DGUS II | EKT050B | √ | × | T5L0 ASIC 5.0-mirefy, 480×854, loko 262K, IPS |

| TA/DGUS II | EKT050C | √ | × | T5L2 ASIC 5.0-mirefy, 1280×720, loko 16.7M, IPS |

| TA/DGUS II | EKT056 | √ | × | T5L1 ASIC 5.6-mirefy, 640×480, loko 16.7M, IPS, |

| TA/DGUS II | EKT057 | √ | × | T5L0 ASIC 5.7-mirefy, 640×480, loko 262K, TN |

| TA/DGUS II | EKT065 | √ | × | T5L0 ASIC 6,5 santimetatra, 640 × 480, loko 262K, TN |

| TA/DGUS II | EKT068 | √ | × | T5L2 ASIC 6,8 santimetatra, 1280×480, loko 16,7M, IPS |

| TA/DGUS II | EKT070A | √ | × | T5L0 ASIC 7.0-mirefy, 800×480, loko 262K, TN |

| TA/DGUS II | EKT070C | √ | √ | T5L2 ASIC 7.0-mirefy, 1024×600, loko 16.7M, IPS |

| TA/DGUS II | EKT070D | √ | × | T5L2 ASIC 7.0-mirefy, 1280×800, loko 16.7M, IPS |

| TA/DGUS II | EKT080A | √ | × | T5L1 ASIC 8.0-mirefy, 800×600, loko 16.7M, TN |

| TA/DGUS II | EKT080B | √ | × | T5L2 ASIC 8.0-mirefy, 1024×768, loko 16.7M, IPS |

| TA/DGUS II | EKT080C | √ | × | T5L2 ASIC 8.0-mirefy, 1280×800, loko 16.7M, IPS |

| TA/DGUS II | EKT084 | √ | × | T5L1 ASIC 8,4 santimetatra, 800 × 600, loko 16,7M, TN |

| TA/DGUS II | EKT088 | √ | × | T5L2 ASIC 8,8 santimetatra, 1920 × 480, loko 16,7M, IPS |

| TA/DGUS II | EKT097 | √ | × | T5L2 ASIC 9,7 santimetatra, 1024 × 768, loko 16,7M, TN |

| TA/DGUS II | EKT101A | √ | × | T5L2 ASIC 10.1-mirefy, 1024×600, loko 16.7M, IPS |

| TA/DGUS II | EKT101B | √ | × | T5L2 ASIC 10.1-mirefy, 1280×800, loko 16.7M, IPS |

●Capacitive touchscreen.

●20 IOs, 4 UARTs, 1 CAN, 2 PWM ary 6 12-bit AD.

●JTAG interface tsara ho an'ny emulation an-tserasera sy ny debugging.

●Fahaizana mamaky sy manoratra ny fari-piainan'ny DGUS, debugging ary misintona mivantana ny tetikasa UI amin'ny alàlan'ny interface USB.

●2 128M-bit SPI NOR Flash interface tsara ary 1 1Gbit SPI NAND Flash interface tsara.

●T5L OS core dia 200MHz 1T haingam-pandeha 8051, ao anatin'izany ny habaka code 64KB, RAM on-chip 32KB, MAC integer 64bit ary mpizara hardware.